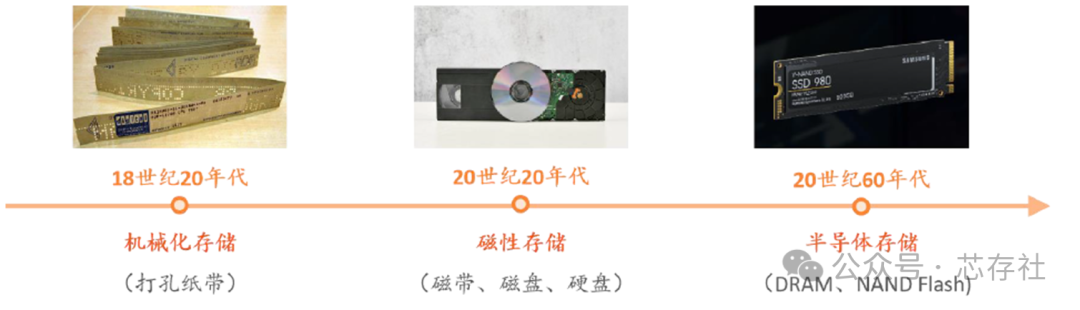

•在5G、AI、AIOT等新兴战略产业的快速发展带动下,信息数据呈现爆发式增长,数据规模从原来的GB、TB、PB上升到EB、ZB级,存储器作为信息数据的存储媒介,其重要性不言而喻,半导体存储作为当前主流存储技术,在经历了半个世纪的发展后,形成了以DRAM和NAND为主的产品构成格局。

•1966年IBM发明的DRAM标志着半导体存储时代的开启,在行业发展的早期,市场主要以DRAM产品为主,当时单颗芯片容量仅为1Kb,现在已扩容至32Gb以上,DRAM存储技术已发展超过半个世纪,技术创新主要以制程推进为主。

•1980年代初入市场的NAND Flash只有4Mb容量,发展至今单芯片可达2Tb,Flash存储技术已发展40余年由2D NAND向3D NAND技术路径演进。

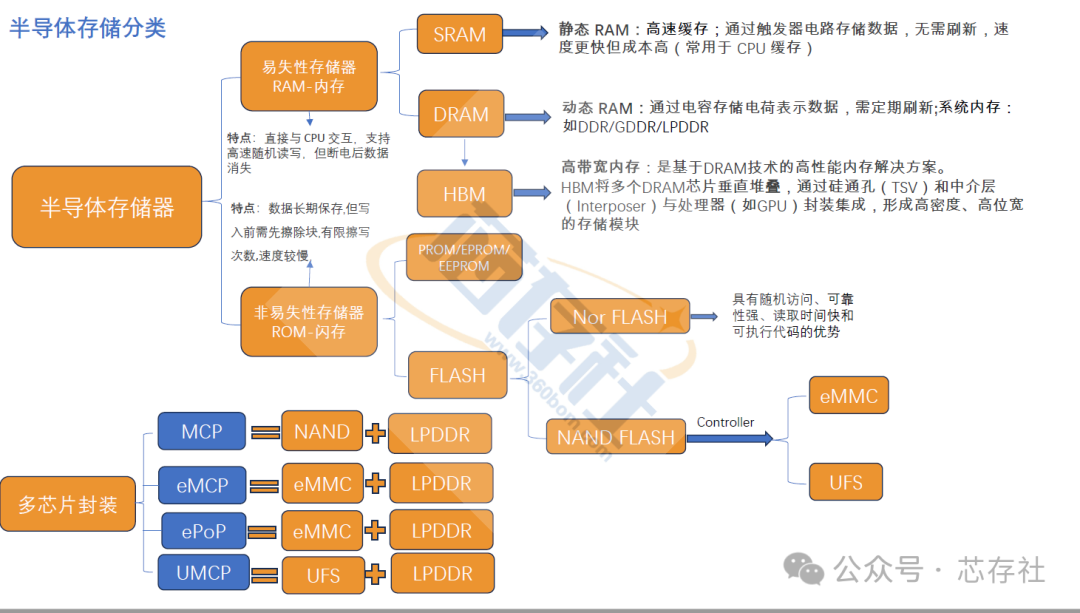

半导体存储也称为存储芯片,根据数据存储原理的不同,半导体存储器可以分为随机存储器(RAM)和只读存储器(ROM)。

RAM是与CPU直接交换数据的内部存储器,可随时进行数据读写且速度较快,断电后保存数据会丢失,是易失性存储器,通常用作操作系统或者其他运行中程序的临时数据存储介质;

ROM是一种只能读取事先所存数据的存储器,断电后也能保存数据,是非易失性存储器,常用于存储各种固定程序和数据。

RAM可进一步细分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。相较于DRAM,SRAM读写速度非常快,但价格较高,通常用作计算机中的高速缓冲存储器,即CPU、GPU中内部L1/L2缓存或外部L2高速缓存,容量只有几十Kb至几十Mb。DRAM常用于计算机中的主存储器,由于结构简单成本相对较低,作为系统内存具有很高的性价比优势。

ROM根据内容写入方式可分为PROM、EPROM、OTPROM、EEPROM和Flash等。Flash又称闪存,是现阶段主流存储器,拥有可擦除可编程的特点,在断电的环境下也能保证数据的保存完整性,成本低且密度大,广泛应用于嵌入式系统中。Flash又可进一步划分为NAND Flash和NOR Flash,NAND Flash是市场主流Flash存储产品,写入和擦除的速度快,存储容量大,是高数据存储密度的理想解决方案;相较于NAND Flash,NOR Flash可以直接在Flash闪存内运行应用程序,容量较小,读取速度快,主要应用于汽车、功能手机、物联网等小容量代码存储。

•按照产品分类DRAM可以细分为DDR、LPDDR、GDDR、HBM等

DDR(Double Data Rate SDRAM,双倍速率同步动态随机存储器)主要应用于PC和服务器上,当前已经发展至第五代,每一代的升级主要体现在工作电压越来越低、芯片容量越来越大、传输速率也越来越快。DDR5于2020年上市,相较于DDR4,DDR5传输速度提升约2倍,同时耗电量降低约20%,当前价格较高成为制约DDR5发展的主要因素,随着产品单价和产能逐步达到市场要求,加上各大厂商的积极推动,DDR5渗透率将进一步提升。

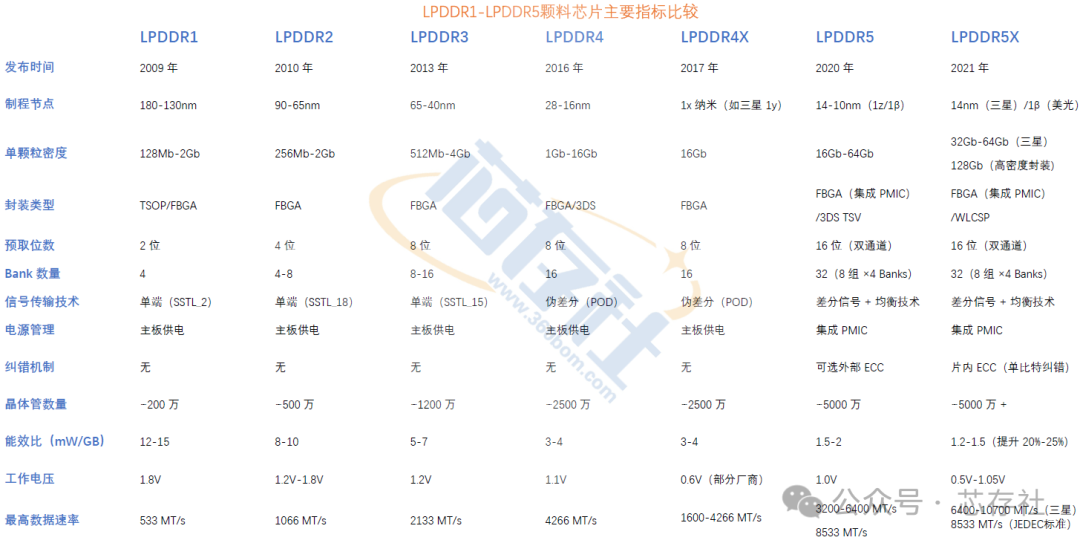

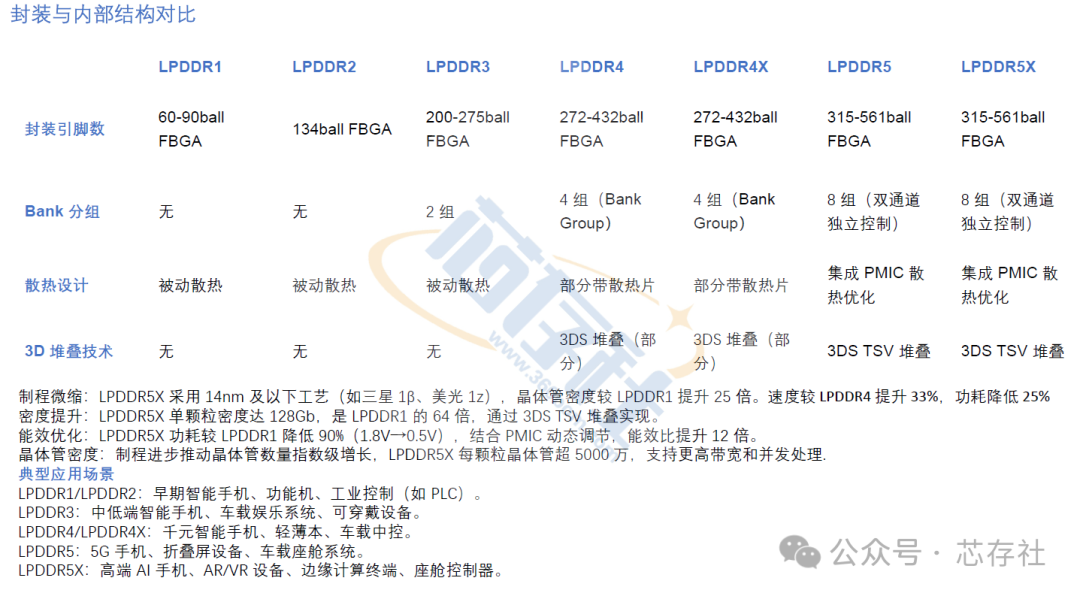

•LPDDR(Low Power DDR,低功耗双信道同步动态随机存取内存)以低功耗和小体积著称,简称“低功耗内存”主要应用于移动式电子产品。为了满足智能手机等移动式电子产品在功耗和体积方面的需求,在DDR的基础上诞生LPDDR,当前LPDDR发展到LPDDR5X,相较上一代标准,LPDDR5X性能提升同样非常显著,拥有更快的速率、更高的带宽和更低的延迟。

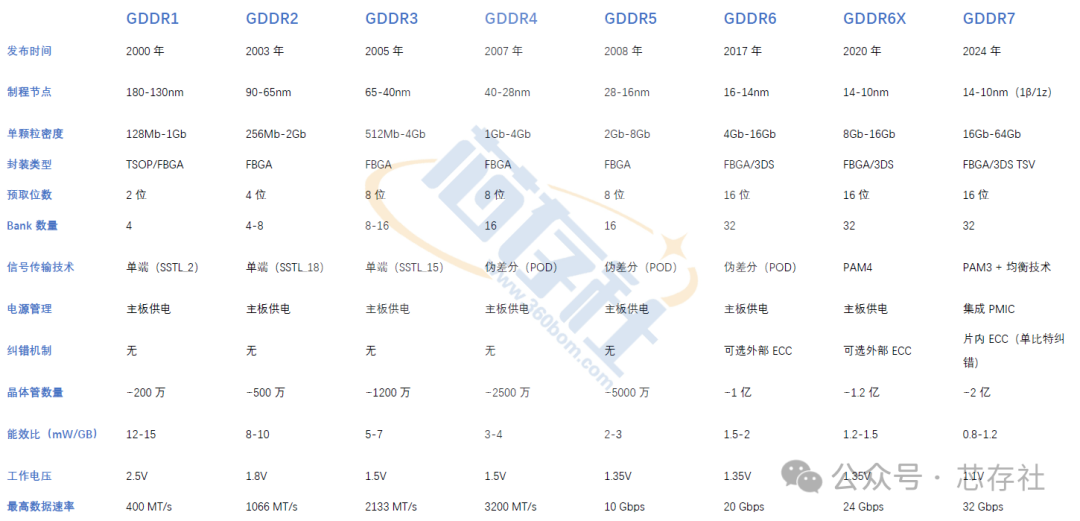

•GDDR(Graphics DDR,绘图用双信道同步动态随机存取内存)专门为高端显示应用所打造,具备高带宽、高延时特点,主要适配于类似显示图像这种需要大数据传输而对时延不敏感的场合,当前GDDR已发展至GDDR7

十纳米级DRAM:第一代1x(18~19nm)、第二代1y(17~18nm)、第三代1z(16~17nm)、第四代1α或1a(14~15nm)、第五代1β或1b(12~13nm)、第六代1γ或1c(11~12nm)、第七代1δ或1d(10~11nm)、第八代1ε(10nm)

第四代1a和第五代1b制程美光反超:三星在1x、1y和1z制程技术领先,并在1a采用EUV,但美光延续采用DUV机台,反而抢先量产1a和1b制程.

1c制程竞争激烈:美光已送样1γDDR5只用一层EUV加速量产并降低成本·SK海力士1c制程2025上半年量产·应用于DDR5、LPDDR6、GDDR7等。三星的1c制程可能2025年下半年量产.

1d制程:2027年左右将量产第七代1d制程、2028年之后将量产第八代1ε制程.

SK海力士(市占4~5成):2025年3月向主要客户提供12层HBM4样品,正与台积电就16层HBM4进行密切合作

三星(市占4成):打算用1c制程DRAM于HBM4之中,也与台合作。

美光(市占1成~2成):HBM4于2026年量产·HBM4E在2027~2028年亮相,采用台积先进的逻辑代工制程技术。

HBM的逻辑控制芯片(Base Die)朝向先进制程发展·HBM4已经从12nm推进到4/5nm·未来HBM5可能采用3nm甚至更先进的制程,以提升数据吞吐量和降低功耗,推动向外部品圆代工模式转移,例如跟台积合作。

HBM堆栈层数8/12层为主流往16/20层迈进,由于封装厚度受限于775微米(um),因此混合键合(HybridBonding)成为一项重要技术。

HBM价格比一般DRAM高数倍(如16 GB HBM3单价约200美元、24 GB HBM3e单价约400美元),2024年全球HBM市场规模近200亿美元,占DRAM整市场约二成,预估2025年占约四成。

下一期我们将整理NAND篇,欢迎大家持续关注。

如需高清电子档请添加微信:benny0078获取。感谢转发,谢谢。