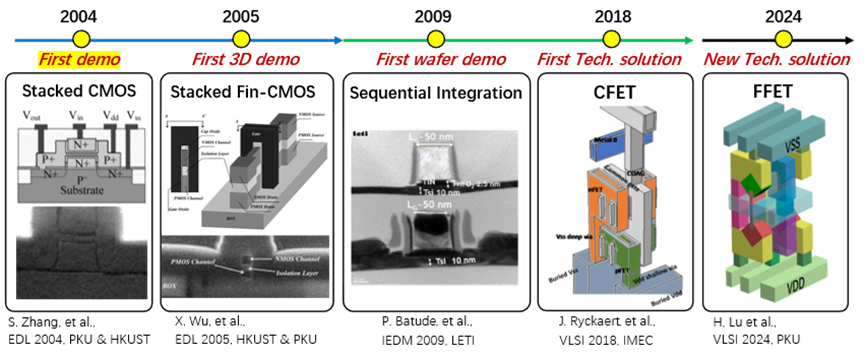

传统二维平面晶体管在纳米级工艺下逐渐面临物理极限,三维堆叠技术成为延续摩尔定律的重要方向。在这一背景下,北京大学微电子学院黄如院士团队在第42届超大规模集成电路研讨会(VLSI 2025)上发布了一种全新三维晶体管结构“倒装堆叠晶体管(Flip FET, FFET)”。该技术首次实现了8层晶体管的三维垂直集成,单位面积逻辑密度较传统FinFET提升3.2倍,功耗降低58%。

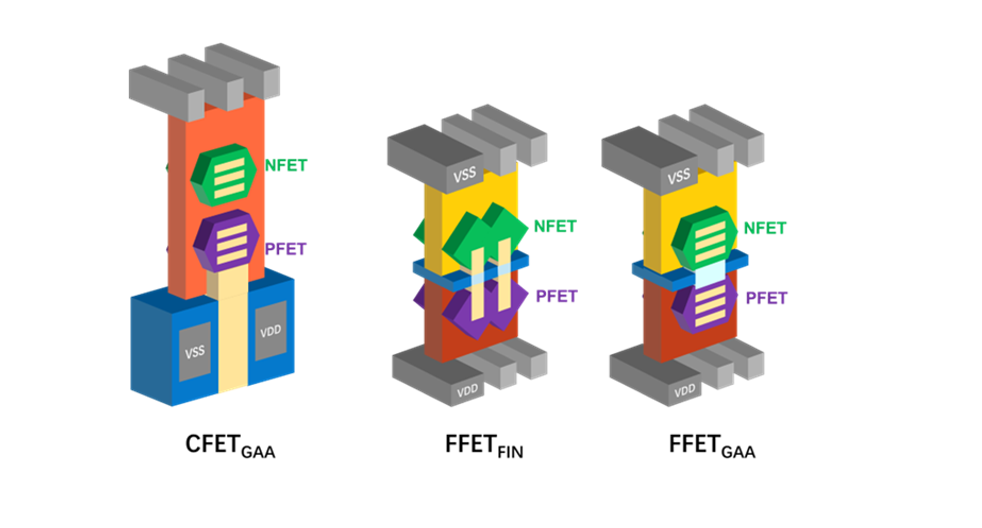

Flip FET通过自对准方式堆叠正面NFET和背面PFET,并结合双面电源/信号互连技术,实现了高密度晶体管集成。研究团队开发了晶圆键合、衬底减薄、背面沟道优化等关键工艺模块,成功验证了Flip FET的正反面器件电性,成为全球首个实现背部集成逻辑晶体管的技术。

实验结果表明,Flip FET的背面PFET性能优异,最小沟长低至30nm,开关比达107,与正面NFET相当。此外,Flip FET还展现出多阈值电压可调性和双面CMOS能力,显著优于传统CFET。针对亚1nm节点,北大团队提出了三代结构创新,包括F3ET、F4ET和CFFET,进一步优化了晶体管密度和性能。

与CFET相比,Flip FET采用双面分离设计,提升了供电效率和设计灵活性,尤其在1nm以下节点更具扩展性。据业内人士透露,Flip FET可兼容现有产线,采用非EUV依赖工艺,降低了产业化门槛,更适应中国大陆产业链现状。

尽管Flip FET展现出巨大潜力,但其量产仍面临诸多挑战。例如,晶圆减薄和背面工艺可能导致翘曲和套刻误差,增加成本并降低良率。此外,晶圆翻转后细间距触点和金属的对准问题仍需解决。