0. ARM异常中断的种类

ARM支持7种异常中断,其中包括复位、未定义指令异常、软中断异常、预取指令中止、数据中止、IRQ、FIQ。

0.1 复位(RESET)(优先级=1)

当处理器复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。复位异常中断通常用在下面几种情况:系统加电时;系统复位时;跳转到复位中断向量处执行成为软复位。

0.2 未定义指令(优先级=6)

当ARM处理器或者是系统中的协处理器认为当前指令未定义时,产生未定义的指令异常中断,可以通过改异常中断机制仿真浮点向量运算。

0.3 软中断(优先级=6)

这是一个由用户定义的中断指令。用于用户模式下的程序调用特权操作指令。在实时操作系统中可以通过该机制实现系统功能调用。

0.4 预取指令终止(Prefech Abort)(优先级=5)

如果处理器预取的指令的地址不存在,或者该地址不允许当前指令访问,当被预取的指令执行时,处理器产生指令预取终止异常中断。

0.5 数据终止(Data Abort)(优先级=2)

如果数据访问指令的目标地址不存在,,或者该地址不允许当前指令访问,处理器产生数据访问终止异常中断。

0.6 IRQ(优先级=4)

当处理器的外部中断请求引脚有效,而且CPSR的寄存器的I控制位被**时,处理器产生外部中断请求异常中断。系统中个外设通过该异常中断请求处理服务。

0.7 FIQ(优先级=3)

当处理器的外部快速中断请求引脚有效,而且CPSR的F控制位被**时,处理器产生外部中断请求异常中断。

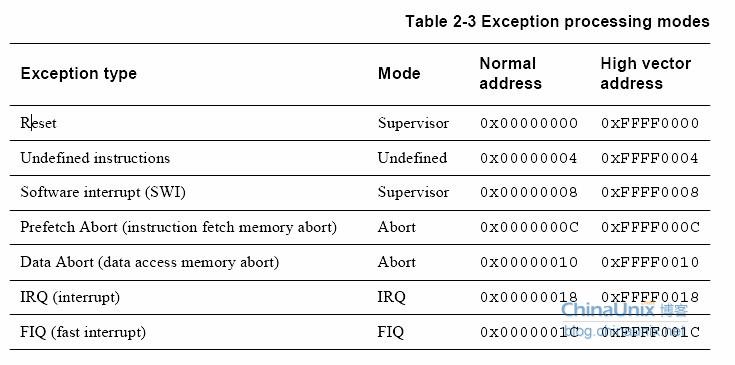

0.8 异常中断向量表及异常中断优先级

中断向量表7个异常中断所在的工作模式和存放地址,见下表。每个异常中断的地址存放了一个跳转指令或者一个向PC寄存器中赋值的数据访问指令。通过这两种指令,程序将跳转到相应的异常中断处理程序处执行。当几个异常中断同时发生时,就必须按照一定的次序来处理这些异常中断,下面继续分析。

ARM的异常处理机制,异常是每一种处理器都必须考虑的问题之一,关键在于如何让处理,返回地址在什么位置都是需要考虑的。一般异常发生后,CPU都会进行一系列的操作,这些操作有一部分是CPU自动完成,有一部分是需要我们程序员完成,在此逐一的分析。

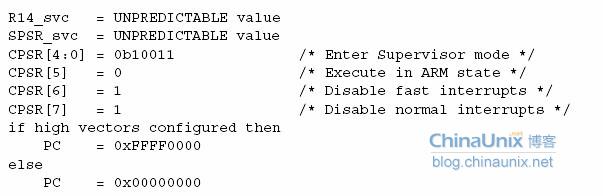

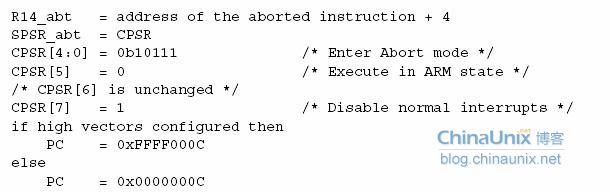

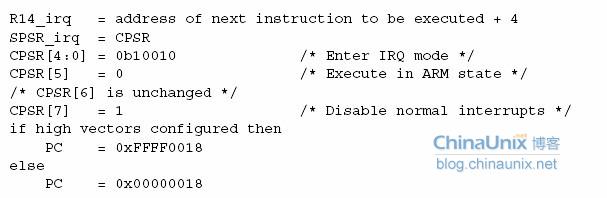

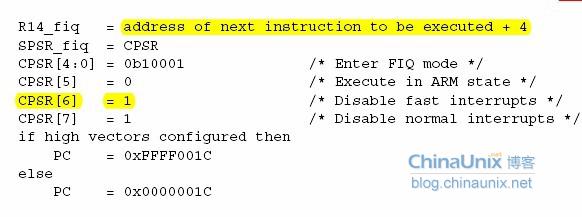

1.CPU自动完成的操作首先说明CPU会自动完成的部分,用ARM结构手册中的代码描述如下:

R14_

SPSR_< exception_mode > = CPSR

CPSR[4:0] = exception mode number

CPSR[5] = 0; //ARM指令

If

CPSR[6] = 1; //只有在复位和FIQ模式下才会关闭FIQ中断

CPSR[7] = 1; //任何异常模式下都会关闭IRQ中断

PC = exception vector address

从上面的代码中我们可以发现CPU自动处理的过程包括如下:

1) 拷贝CPSR到SPSR_

2) 设置适当的CPSR位: 改变处理器状态进入ARM状态;改变处理器模式进入相应的异常模式;设置中断禁止位禁止相应中断。

3) 更新LR_

4) 设置PC到相应的异常向量

以上的操作都是CPU自动完成,然后CPU跳转到程序员定义的异常处理程序(函数),处理完成后返回之前的工作模式,此时的异常返回地址是需要我们留意的地方。

2.异常返回地址问题不同的异常模式返回地址存在差异,这主要是因为各种异常的产生机理存在差别。这样我们需要在进入异常处理函数之前或者异常返回前调整返回地址,一般采用进入异常处理函数前进行手动调整。下面给出了每一种异常时链接寄存器R14保存的值,根据R14的值就可以知道怎样实现地址的返回,其中也包含了CPU自动处理的部分。

2.1 复位异常:

可以看出该模式下的先对来说返回地址也比较简单,不需要做太多的描述。

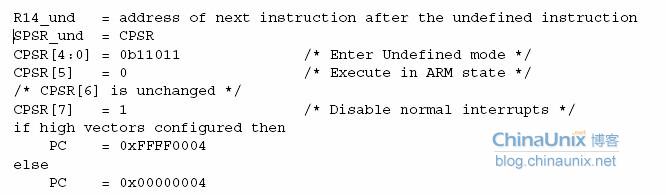

2.2 未定义的指令异常:

返回的方式也比较简单:

MOVS PC, R14

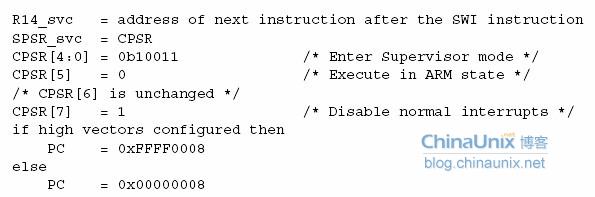

2.3软中断异常:

返回的方式也比较简单:

MOVS PC, R14

2.4 预取指令中止异常:

返回需要做下面的调整:

SUBS PC, R14, #4

2.5 数据中止

返回地址需要做下面的调整:

如果需要重新访问数据则:SUBS PC, R14, #8

如果不需要重新访问数据则:SUBS PC, R14, #4

2.6 IRQ中断的处理过程:

返回地址需要做下面的调整: SUBS PC,R14,#4

2.7 FIQ中断:

返回地址需要做下面的调整: SUBS PC, R14 ,#4

从上面的代码可以知道,对于每一种异常,保存的返回地址都是不一样的,一般都需要我们手动的跳转,当然调整的时机也需要我们选择,是在进入处理前跳转还是返回时调整都是需要程序员控制。

3.异常返回地址的再次说明

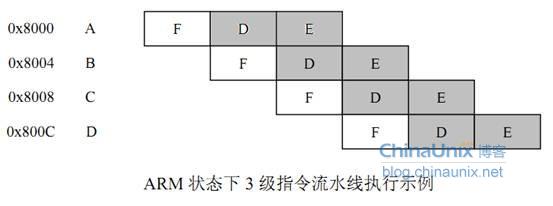

在ARM Developer Suite Developer Guide中对ARM处理器的异常处理操作提供能更加详细的解释,每一种异常下的处理方式如下文描述:异常返回时另一个非常重要的问题是返回地址的确定,在前面曾提到进入异常时处理器会有一个保存LR 的动作,但是该保存值并不一定是正确的返回地址,下面以一个简单的指令执行流水状态图来对此加以说明。

我们知道在ARM 架构里,PC值指向当前执行指令的地址加8处,也就是说, 当执行指令A(地址0x8000)时,PC 等于指令C 的地址(0x8008)。假如指令A 是“BL”指令,则当执行该指令时,会把PC(=0x8008)保存到LR 寄存器里面,但是接下去处理器会马上对LR 进行一个自动的调整动作:LR=LR-0x4。这样,最终保存在 LR 里面的是 B 指令的地址,所以当从 BL 返回时,LR 里面正好是正确的返回地址。同样的调整机制在所有LR自动保存操作中都存在,比如进入中断响应时,处理器所做的LR 保存中,也进行了一次自动调整,并且调整动作都是LR=LR-0x4。

下面,我们对不同类型的异常的返回地址依次进行说明:假设在指令A 处(地址0x8000)发生了异常,进入异常响应后,LR 上经过调整保存的地址值应该是B 的地址0x8004。

3.1 如果发生的是软件中断,即A 是“SWI”指令

异常是由指令本身引起的,从 SWI 中断返回后下一条执行指令就是B,正好是LR 寄存器保存的地址, 所以只要直接把LR 恢复给PC。

MOVS pc, lr

3.2 发生的是Undefined instruction异常

异常是由指令本身引起的,从异常返回后下一条执行指令就是B,正好是LR 寄存器保存的地址, 所以只要直接把LR 恢复给PC。

MOVS pc, lr

3.3 发生的是IRQ或FIQ中断

因为指令不可能被中断打断,所以A指令执行完以后才能响应中断,此时PC已更新,指向指令D的地址(地址0x800C),LR 上经过调整保存的地址值是C 的地址0x8008。中断返回后应该执行B指令,所以返回操作是:

SUBS pc, lr, #4

3.4 发生的是Prefetch Abort异常

该异常并不是处理器试图从一个非法地址取指令时触发,取出的指令只是被标记为非法,按正常处理流程放在流水线上,在执行阶段触发Prefetch Abort异常,此时LR 上经过调整保存的地址值是B 的地址0x8004。异常返回应该返回到A指令,尝试重新取指令,所以返回操作是:

SUBS pc, lr, #4

3.5 发生的是“Data Abort”

CPU访问存储器时触发该异常,此时PC指向指令D的地址(地址0x800C),LR 上经过调整保存的地址值是C 的地址0x8008。异常返回后,应回到指令A,尝试重新操作存储器,所以返回操作是:

SUBS pc, lr, #8

以上就是ARM异常的CPU操作部分,接下来就是程序员应该完成的操作。

4.程序员需要做的事

1) 由于CPU会自动跳转到对应的异常向量中,因此只需要在在各个异常向量中存放对应的操作,最简单的都是存放一个B指令跳转到对应的异常处理函数的操作即可。但由于B指令的跳转返回只有+-32M,而异常处理函数的地址可能会超过+-32M,因此可以采用另一种方式实现方式:在异常向量中保存一条指令LDR PC [addr],其中的addr中就保存了异常处理函数的地址,当然addr的相对地址要小于+-32M。这样也就解决了跳转范围的问题。

2) 接下来就是异常处理函数对应的操作,可以在进入异常处理之前就进行返回地址的调整,这样后面就不用进行处理啦,当然也可以在返回过程中